# E-NOTES ON DIGITAL ELECTRONICS

3<sup>rd</sup> semester Branch-Computer Engineering

# MODULE - 1 Number Systems

## **Understanding Decimal Numbers**

- ° Decimal numbers are made of decimal digits: (0,1,2,3,4,5,6,7,8,9)

- ° Decimal number representation:

- $8653 = 8x10^3 + 6x10^2 + 5x10^1 + 3x10^0$

- ° What about fractions?

- $97654.35 = 9x10^4 + 7x10^3 + 6x10^2 + 5x10^1 + 4x10^0 + 3x10^{-1} + 5x10^{-2}$

- In formal notation ->  $(97654.35)_{10}$

- ° Why do we use 10 digits?

## **Understanding Binary Numbers**

- ° Binary numbers are made of <u>binary digits</u> (bits):

- 0 and 1

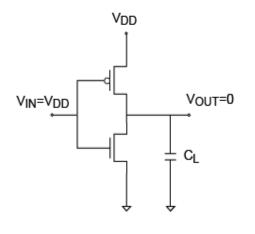

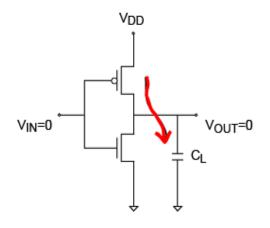

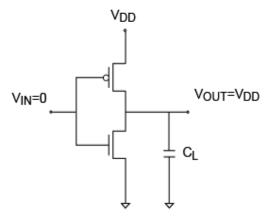

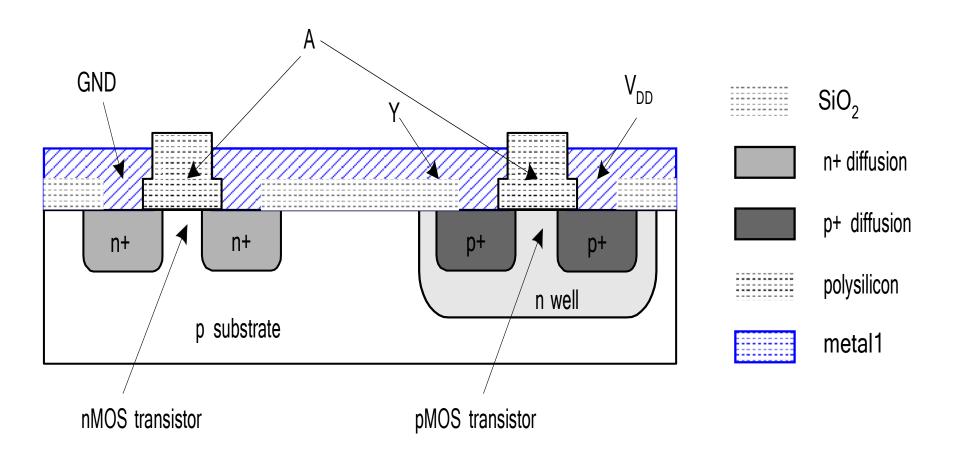

- Output

Output

Output

Description

Output

Description

Output

Description

Description

Output

Description

De

- $(1011)_2 = 1x2^3 + 0x2^2 + 1x2^1 + 1x2^0 = (11)_{10}$

- ° What about fractions?

- $(110.10)_2 = 1x2^{2} + 1x2^{1} + 0x2^{0} + 1x2^{-1} + 0x2^{-2}$

- ° Groups of eight bits are called a byte

- (11001001)<sub>2</sub>

- ° Groups of four bits are called a *nibble*.

- $(1101)_2$

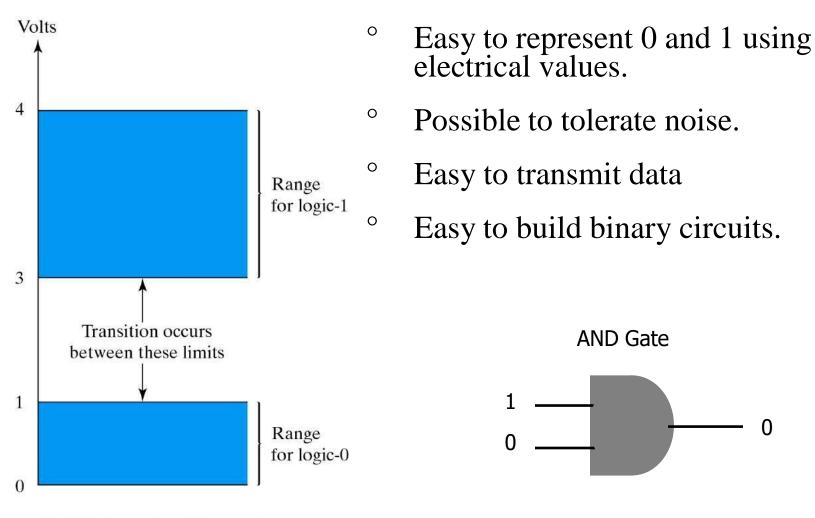

## Why Use Binary Numbers?

Fig. 1-3 Example of binary signals

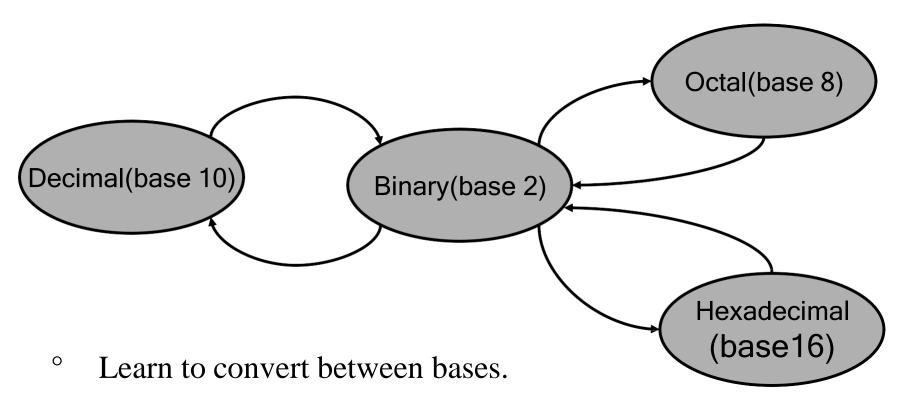

## **Conversion Between Number Bases**

Conversion demonstrated in next slides

## Convert an Integer from Decimal to Another Base

#### For each digit position:

- 1. Divide decimal number by the base (e.g. 2)

- 2. The remainder is the lowest-order digit

- 3. Repeat first two steps until no divisor remains.

#### Example for $(13)_{10}$ :

| Integer<br>Quotien |              | Remainder        | Coefficient                 |

|--------------------|--------------|------------------|-----------------------------|

| 6                  | +            | 1/2              | $a_0 = 1$                   |

| 3                  | +            | 0                | $a_1 = 0$                   |

| 1                  | +            | 1/2              | $a_{2} = 1$                 |

| 0                  | +            | 1/2              | a <sub>3</sub> = 1          |

|                    | Quotien<br>6 | Quotient 6 + 3 + | Quotient  6 + ½ 3 + 0 1 + ½ |

Answer

$$(13)_{10} = (a_3 a_2 a_1 a_0)_2 = (1101)_2$$

## **Convert an Fraction from Decimal to Another Base**

#### For each digit position:

- 1. Multiply decimal number by the base (e.g. 2)

- 2. The *integer* is the highest-order digit

- 3. Repeat first two steps until fraction becomes zero.

Example for  $(0.625)_{10}$ :

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Integer |   | Fraction     | Coefficient                                |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|---|--------------|--------------------------------------------|

| 0.625 x 2 = 0.250 x 2 =                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 1       | + | 0.25<br>0.50 | a <sub>-1</sub> = 1                        |

| $0.500 \times 2 = 0.500 \times 2 = 0.50$ | 1       | + | 0.30         | a <sub>-2</sub> = 0<br>a <sub>-3</sub> = 1 |

Answer

$$(0.625)_{10} = (0.a_{-1} a_{-2} a_{-3})_2 = (0.101)_2$$

## **The Growth of Binary Numbers**

| n | <b>2</b> <sup>n</sup> |

|---|-----------------------|

| 0 | 2 <sup>0</sup> =1     |

| 1 | 2 <sup>1</sup> =2     |

| 2 | 2 <sup>2</sup> =4     |

| 3 | 2 <sup>3</sup> =8     |

| 4 | 2 <sup>4</sup> =16    |

| 5 | 2 <sup>5</sup> =32    |

| 6 | 2 <sup>6</sup> =64    |

| 7 | 2 <sup>7</sup> =128   |

| n  | <b>2</b> <sup>n</sup> |

|----|-----------------------|

| 8  | 2 <sup>8</sup> =256   |

| 9  | 2 <sup>9</sup> =512   |

| 10 | 2 <sup>10</sup> =1024 |

| 11 | 211=2048              |

| 12 | 2 <sup>12</sup> =4096 |

| 20 | 2 <sup>20</sup> =1M   |

| 30 | 2 <sup>30</sup> =1G   |

| 40 | 2 <sup>40</sup> =1T   |

Mega

Giga

Tera

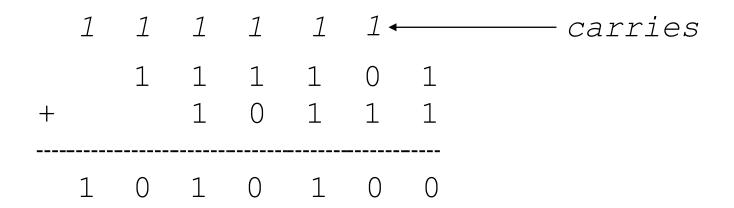

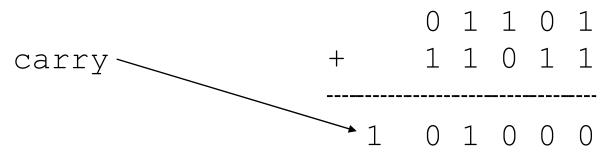

## **Binary Addition**

- ° Binary addition is very simple.

- ° This is best shown in an example of adding two binary numbers...

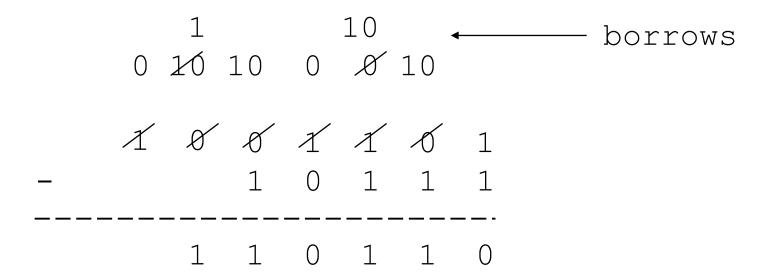

## **Binary Subtraction**

- ° We can also perform subtraction (with borrows in place of carries).

- $^{\circ}$  Let's subtract  $(10111)_2$  from  $(1001101)_2$ ...

## **Binary Multiplication**

Obligation is much the same as decimal multiplication, except that the multiplication operations are much simpler...

| Χ |        |             | 1                | 0                | 1           | 1<br>1 | 1 0 |

|---|--------|-------------|------------------|------------------|-------------|--------|-----|

| 1 | 0<br>0 | 1<br>0<br>1 | 0<br>0<br>0<br>1 | 0<br>1<br>0<br>1 | 0<br>1<br>0 | 0      | 0   |

| 1 | 1      | 1           | 0                | 0                | 1           | 1      | 0   |

## **Convert an Integer from Decimal to Octal**

#### For each digit position:

- 1. Divide decimal number by the base (8)

- 2. The remainder is the lowest-order digit

- 3. Repeat first two steps until no divisor remains.

#### **Example for** $(175)_{10}$ **:**

|         | Integer |    | Remainder | Coefficient |

|---------|---------|----|-----------|-------------|

| •       | Quotie  | nt |           |             |

| 175/8 = | 21      | +  | 7/8       | $a_0 = 7$   |

| 21/8 =  | 2       | +  | 5/8       | $a_1 = 5$   |

| 2/8 =   | 0       | +  | 2/8       | $a_{2} = 2$ |

Answer

$$(175)_{10} = (a_2 a_1 a_0)_2 = (257)_8$$

## **Understanding Octal Numbers**

- ° Octal numbers are made of octal digits: (0,1,2,3,4,5,6,7)

- ° Octal number representation:

- $(4536)_8 = 4x8^3 + 5x8^2 + 3x8^1 + 6x8^0 = (1362)_{10}$

- ° What about fractions?

- $(465.27)_8 = 4x8^2 + 6x8^1 + 5x8^0 + 2x8^{-1} + 7x8^{-2}$

- ° Octal numbers don't use digits 8 or 9

## **Understanding Hexadecimal Numbers**

- ° Hexadecimal numbers are made of <u>16</u> digits:

- (0,1,2,3,4,5,6,7,8,9,A, B, C, D, E, F)

- ° hex number representation:

- $(3A9F)_{16} = 3x16^3 + 10x16^2 + 9x16^1 + 15x16^0 = 14999_{10}$

- ° What about fractions?

- $(2D3.5)_{16} = 2x16^{2} + 13x16^{1} + 3x16^{0} + 5x16^{-1} = 723.3125_{10}$

- Note that *each* hexadecimal digit can be represented with four bits.

- $(1110)_2 = (E)_{16}$

- ° Groups of four bits are called a *nibble*.

- (1110)<sub>2</sub>

## **Putting It All Together**

| Decimal | Binary | Octal  | Hexadecimal |

|---------|--------|--------|-------------|

| 0       | 0      | O      | 0           |

| 1       | 1      | 1      | 1           |

| 2       | 10     | 2      | 2           |

| 3       | 11     | 3      | 3           |

| 4       | 100    | 3<br>4 | 4           |

| 5       | 101    | 5      | 5           |

| 6       | 110    | 6      | 6           |

| 7       | 111    | 7      | 7           |

| 8       | 1000   | 10     | 8           |

| 9       | 1001   | 11     | 9           |

| 10      | 1010   | 12     | Α           |

| 11      | 1011   | 13     | В           |

| 12      | 1100   | 14     | C           |

| 13      | 1101   | 15     | D           |

| 14      | 1110   | 16     | E           |

| 15      | 1111   | 17     | F           |

- Binary, octal, and hexadecimal similar

- Easy to build circuits to operate on these representations

- Possible to convert between the three formats

## **Converting Between Base 16 and Base 2**

$$3A9F_{16} = 0011 1010 1001 1111_2$$

3 A 9 F

- ° Determine 4-bit value for each hex digit

- $^{\circ}$  Note that there are  $2^4 = 16$  different values of four bits

- ° Easier to read and write in hexadecimal.

- ° Representations are equivalent!

## **Converting Between Base 16 and Base 8**

$$3A9F_{16} = 0011 \quad 1010 \quad 1001 \quad 1111_{2}$$

$$3 \quad A \quad 9 \quad F$$

$$35237_{8} = 011 \quad 101 \quad 010 \quad 011 \quad 111_{2}$$

$$3 \quad 5 \quad 2 \quad 3 \quad 7$$

- 1. Convert from Base 16 to Base 2

- 2. Regroup bits into groups of three starting from right

- 3. Ignore leading zeros

- 4. Each group of three bits forms an octal digit.

## **How To Represent Signed Numbers**

- Plus and minus sign used for decimal numbers: 25 (or +25), -16, etc.

- For computers, desirable to represent everything as *bits*.

- Three types of signed binary number representations: signed magnitude, 1's complement, 2's complement.

- In each case: left-most bit indicates sign: positive (0) or negative (1).

#### Consider signed magnitude:

## **One's Complement Representation**

- The one's complement of a binary number involves inverting all bits.

- 1's comp of 00110011 is 11001100

- 1's comp of 10101010 is 01010101

- For an n bit number N the 1's complement is  $(2^{n}-1) N$ .

- Called diminished radix complement by Mano since 1's complement for base (radix 2).

- To find negative of 1's complement number take the 1's complement.

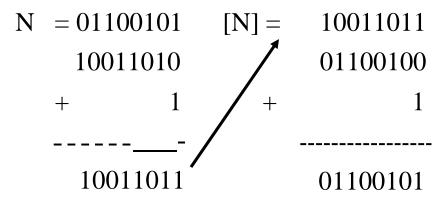

## **Two's Complement Representation**

- The two's complement of a binary number involves inverting all bits and adding 1.

- 2's comp of 00110011 is 11001101

- 2's comp of 10101010 is 01010110

- For an n bit number N the 2's complement is  $(2^{n}-1) N + 1$ .

- Called radix complement by Mano since 2's complement for base (radix 2).

- To find negative of 2's complement number take the 2's complement.

## **Two's Complement Shortcuts**

- ° Algorithm 1 − Simply complement each bit and then add 1 to the result.

- Finding the 2's complement of (01100101)<sub>2</sub> and of its 2's complement...

- ° Algorithm 2 − Starting with the least significant bit, copy all of the bits up to and including the first 1 bit and then complementing the remaining bits.

- N = 0 1 1 0 0 1 0 1[N] = 1 0 0 1 1 0 1 1

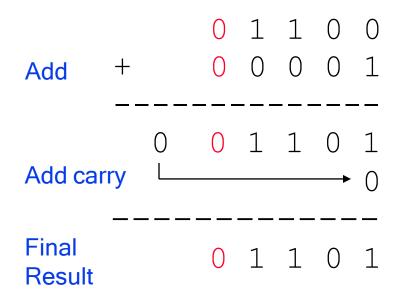

## 1's Complement Addition

- ° Using 1's complement numbers, adding numbers is easy.

- $^{\circ}$  For example, suppose we wish to add +(1100)<sub>2</sub> and +(0001)<sub>2</sub>.

- ° Let's compute  $(12)_{10} + (1)_{10}$ .

- $(12)_{10} = +(1100)_2 = 01100_2$  in 1's comp.

- $(1)_{10} = +(0001)_2 = 00001_2$  in 1's comp.

Step 1: Add binary numbers

Step 2: Add carry to low-order bit

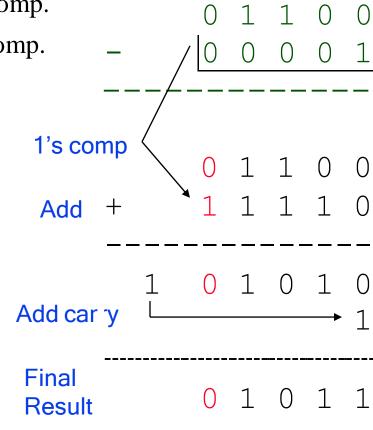

## 1's Complement Subtraction

- ° Using 1's complement numbers, subtracting numbers is also easy.

- $^{\circ}$  For example, suppose we wish to subtract +(0001)<sub>2</sub> from +(1100)<sub>2</sub>.

- ° Let's compute  $(12)_{10}$   $(1)_{10}$ .

- $(12)_{10} = +(1100)_2 = 01100_2$  in 1's comp.

- $(-1)_{10} = -(0001)_2 = 111110_2$  in 1's comp.

Step 1: Take 1's complement of 2<sup>nd</sup> operand

Step 2: Add binary numbers

Step 3: Add carry to low order bit

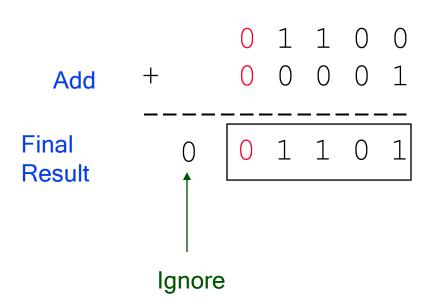

## 2's Complement Addition

- ° Using 2's complement numbers, adding numbers is easy.

- $^{\circ}$  For example, suppose we wish to add +(1100)<sub>2</sub> and +(0001)<sub>2</sub>.

- $^{\circ}$  Let's compute  $(12)_{10} + (1)_{10}$ .

- $(12)_{10} = +(1100)_2 = 01100_2$  in 2's comp.

- $(1)_{10} = +(0001)_2 = 00001_2$  in 2's comp.

Step 1: Add binary numbers

Step 2: Ignore carry bit

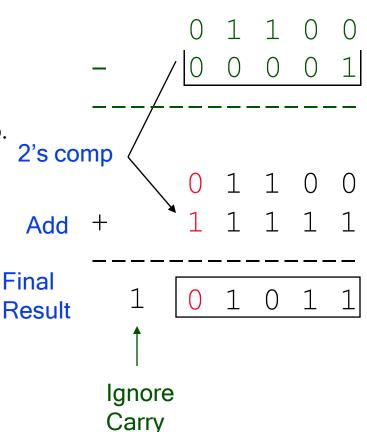

## 2's Complement Subtraction

- Using 2's complement numbers, follow steps for subtraction

- ° For example, suppose we wish to subtract  $+(0001)_2$  from  $+(1100)_2$ .

- $^{\circ}$  Let's compute  $(12)_{10}$   $(1)_{10}$ .

- $(12)_{10} = +(1100)_2 = 01100_2$  in 2's comp.

- $(-1)_{10} = -(0001)_2 = 11111_2$  in 2's comp.

- Step 1: Take 2's complement of 2<sup>nd</sup> operand

- Step 2: Add binary numbers

- Step 3: Ignore carry bit

## 2's Complement Subtraction: Example #2

- ° Let's compute  $(13)_{10} (5)_{10}$ .

- $(13)_{10} = +(1101)_2 = (01101)_2$

- $(-5)_{10} = -(0101)_2 = (11011)_2$

- Adding these two 5-bit codes...

Oiscarding the carry bit, the sign bit is seen to be zero, indicating a correct result. Indeed,

$$(01000)_2 = +(1000)_2 = +(8)_{10}$$

.

## 2's Complement Subtraction: Example #3

$^{\circ}$  Let's compute  $(5)_{10} - (12)_{10}$ .

•

$$(-12)_{10} = -(1100)_2 = (10100)_2$$

•

$$(5)_{10}$$

=  $+(0101)_2$  =  $(00101)_2$

° Adding these two 5-bit codes...

° Here, there is no carry bit and the sign bit is 1. This indicates a negative result, which is what we expect.  $(11001)_2 = -(7)_{10}$ .

## **Boolean Algebra**

## **Overview**

- ° Logic functions with 1's and 0's

- Building digital circuitry

- ° Truth tables

- ° Logic symbols and waveforms

- ° Boolean algebra

- ° Properties of Boolean Algebra

- Reducing functions

- Transforming functions

## **Digital Systems**

Analysis problem:

- Determine binary outputs for each combination of inputs

- Design problem: given a task, develop a circuit that accomplishes the task

- Many possible implementation

- Try to develop "best" circuit based on some criterion (size, power, performance, etc.)

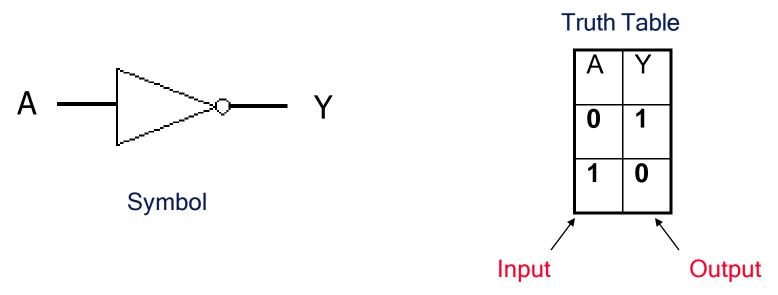

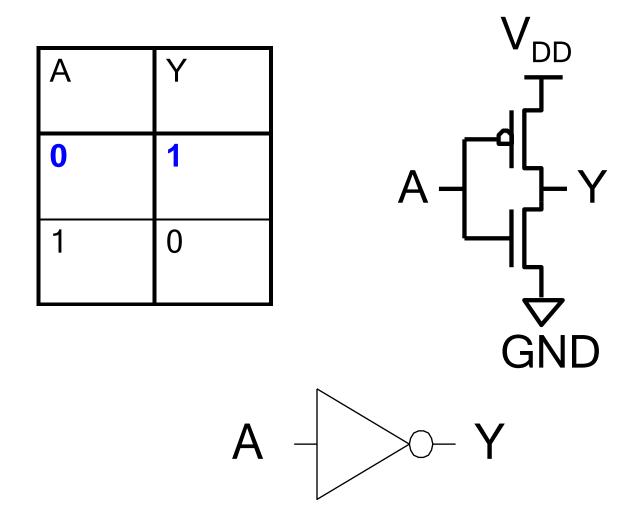

## **Describing Circuit Functionality: Inverter**

- ° Basic logic functions have symbols.

- ° The same functionality can be represented with truth tables.

- Truth table completely specifies outputs for all input combinations.

- ° The above circuit is an inverter.

- An input of 0 is inverted to a 1.

- An input of 1 is inverted to a 0.

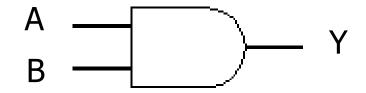

#### **The AND Gate**

- ° This is an AND gate.

- So, if the two inputs signals are asserted (high) the output will also be asserted.

Otherwise, the output will be deasserted (low).

#### **Truth Table**

| А | В | Υ |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 1 |

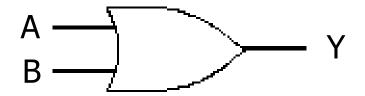

## **The OR Gate**

- ° This is an OR gate.

- So, if either of the two input signals are asserted, or both of them are, the output will be asserted.

| А | В | Υ |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 1 |

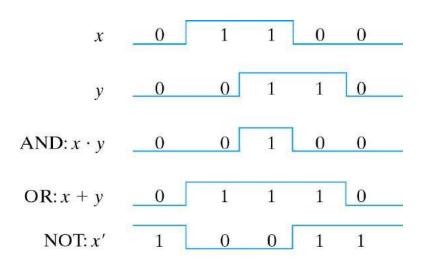

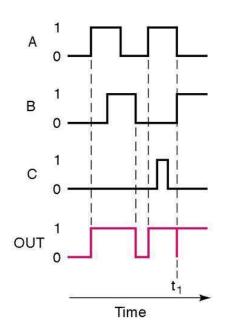

## **Describing Circuit Functionality: Waveforms**

Fig. 1-5 Input-output signals for gates

| 7.1.12 3.3.13 |   |   |

|---------------|---|---|

| А             | В | Υ |

| 0             | 0 | 0 |

| 0             | 1 | 0 |

| 1             | 0 | 0 |

| 1             | 1 | 1 |

**AND Gate**

- ° Waveforms provide another approach for representing functionality.

- ° Values are either high (logic 1) or low (logic 0).

- ° Can you create a truth table from the waveforms?

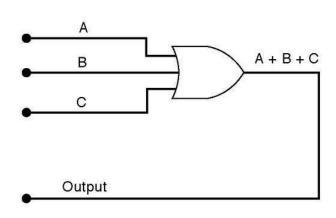

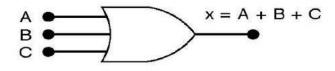

## **Consider three-input gates**

#### 3 Input OR Gate

| 0 | 0 | 0 | 0 |

|---|---|---|---|

| 0 | 0 | 1 | 1 |

| 0 | 1 | 0 | 1 |

| 0 | 1 | 1 | 1 |

| 1 | 0 | 0 | 1 |

| 1 | 0 | 1 | 1 |

| 1 | 1 | 0 | 1 |

| 1 | 1 | 1 | 1 |

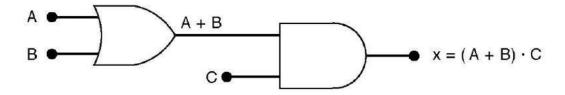

#### **Ordering Boolean Functions**

- ° How to interpret A•B+C?

- Is it A•B ORed with C?

- Is it A ANDed with B+C?

- ° Order of precedence for Boolean algebra: AND before OR.

- ° Note that parentheses are needed here:

## **Boolean Algebra**

- ° A Boolean algebra is defined as a closed algebraic system containing a set K or two or more elements and the two operators, . and +.

- ° Useful for identifying and minimizing circuit functionality

- ° Identity elements

- a + 0 = a

- $a \cdot 1 = a$

- ° 0 is the identity element for the + operation.

- ° 1 is the identity element for the . operation.

### **Commutativity and Associativity of the Operators**

° The Commutative Property:

For every a and b in K,

- a + b = b + a

- $a \cdot b = b \cdot a$

- ° The Associative Property:

For every a, b, and c in K,

- a + (b + c) = (a + b) + c

- $a \cdot (b \cdot c) = (a \cdot b) \cdot c$

### **Distributivity of the Operators and Complements**

° The Distributive Property:

For every a, b, and c in K,

- $a + (b \cdot c) = (a + b) \cdot (a + c)$

- a.(b+c)=(a.b)+(a.c)

- The Existence of the Complement:

For every a in K there exists a unique element called a' (*complement of a*) such that,

- a + a' = 1

- $a \cdot a' = 0$

- ° To simplify notation, the . operator is frequently omitted. When two elements are written next to each other, the AND (.) operator is implied...

- $a + b \cdot c = (a + b) \cdot (a + c)$

- a + bc = (a + b)(a + c)

### **Duality**

- ° The principle of duality is an important concept. This says that if an expression is valid in Boolean algebra, the dual of that expression is also valid.

- ° To form the dual of an expression, replace all + operators with . operators, all . operators with + operators, all ones with zeros, and all zeros with ones.

- ° Form the dual of the expression

$$a + (bc) = (a + b)(a + c)$$

° Following the replacement rules...

$$a(b+c) = ab + ac$$

° Take care not to alter the location of the parentheses if they are present.

#### **Involution**

° This theorem states:

$$a^{\prime\prime} = a$$

- $^{\circ}$  Remember that aa' = 0 and a+a'=1.

- Therefore, a' is the complement of a and a is also the complement of a'.

- As the complement of a' is unique, it follows that a''=a.

- ° Taking the double inverse of a value will give the initial value.

## **Absorption**

° This theorem states:

$$a + ab = a$$

$a(a+b) = a$

° To prove the first half of this theorem:

$$a + ab = a \cdot 1 + ab$$

=  $a (1 + b)$

=  $a (b + 1)$

=  $a (1)$

### **DeMorgan's Theorem**

° A key theorem in simplifying Boolean algebra expression is DeMorgan's Theorem. It states:

$$(a + b)' = a'b'$$

$(ab)' = a' + b'$

° Complement the expression

$$a(b + z(x + a'))$$

and simplify.

$$(a(b+z(x + a')))' = a' + (b + z(x + a'))'$$

$$= a' + b'(z(x + a'))'$$

$$= a' + b'(z' + (x + a')')$$

$$= a' + b'(z' + x'a'')$$

$$= a' + b'(z' + x'a)$$

### **Summary**

- Basic logic functions can be made from AND, OR, and NOT (invert) functions

- The behavior of digital circuits can be represented with waveforms, truth tables, or symbols

- ° Primitive gates can be combined to form larger circuits

- Boolean algebra defines how binary variables can be combined

- ° Rules for associativity, commutativity, and distribution are similar to algebra

- ° DeMorgan's rules are important.

- Will allow us to reduce circuit sizes.

# More Logic Functions: NAND, NOR, XOR

#### **Overview**

- ° More 2-input logic gates (NAND, NOR, XOR)

- ° Extensions to 3-input gates

- ° Converting between sum-of-products and NANDs

- SOP to NANDs

- NANDs to SOP

- ° Converting between sum-of-products and NORs

- SOP to NORs

- NORs to SOP

- ° Positive and negative logic

- We use primarily positive logic in this course.

#### Logic functions of N variables

- ° Each truth table represents one possible function (e.g. AND, OR)

- $^{\circ}$  If there are N inputs, there are  $2^2$

- ° For example, is N is 2 then there are 16 possible truth tables.

- ° So far, we have defined 2 of these functions

- 14 more are possible.

- Why consider new functions?

- Cheaper hardware, more flexibility.

| X | У | G |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 1 |

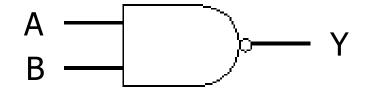

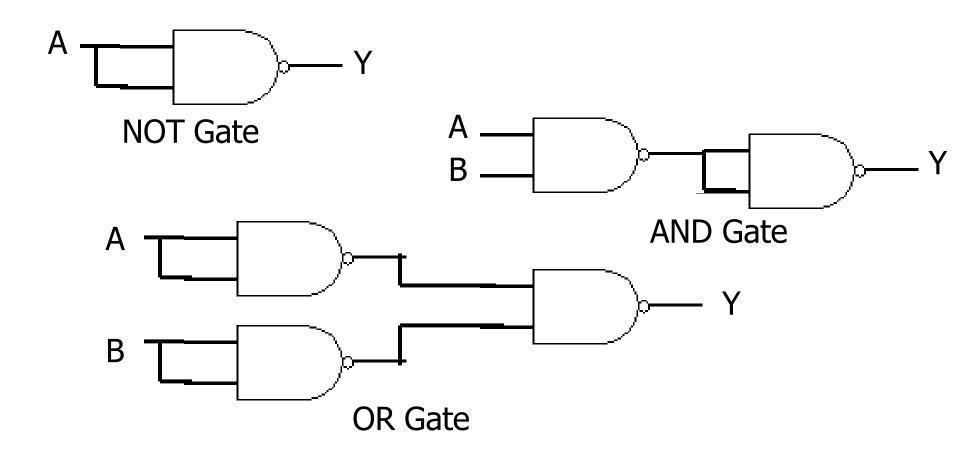

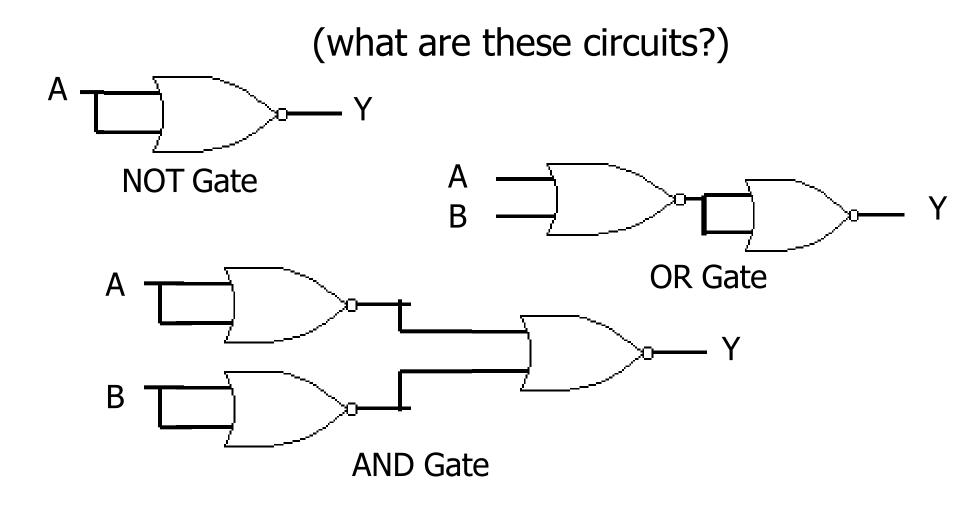

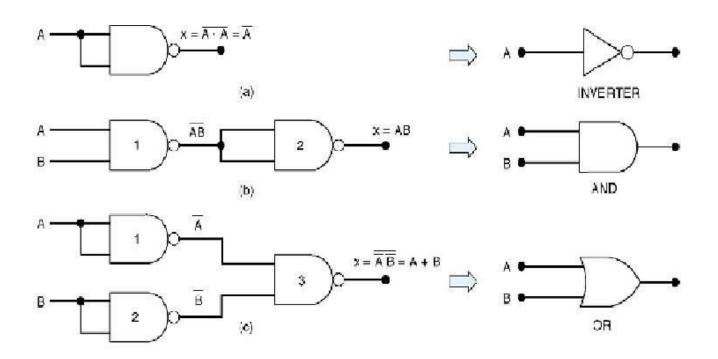

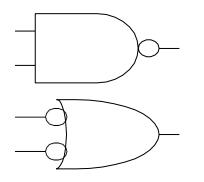

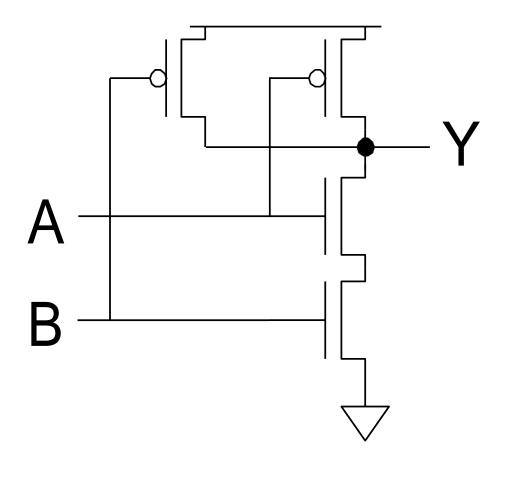

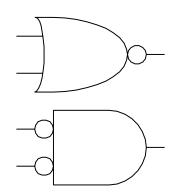

#### The NAND Gate

- ° This is a NAND gate. It is a combination of an AND gate followed by an inverter. Its truth table shows this...

- NAND gates have several interesting properties...

- NAND(a,a)=(aa)'=a'=NOT(a)

- NAND'(a,b)=(ab)''=ab=AND(a,b)

- NAND(a',b')=(a'b')'=a+b=OR(a,b)

| А | В | Υ |

|---|---|---|

| 0 | 0 | 1 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

#### The NAND Gate

- ° These three properties show that a NAND gate with both of its inputs driven by the same signal is equivalent to a NOT gate

- A NAND gate whose output is complemented is equivalent to an AND gate, and a NAND gate with complemented inputs acts as an OR gate.

- ° Therefore, we can use a NAND gate to implement all three of the *elementary operators* (AND,OR,NOT).

- ° Therefore, ANY switching function can be constructed using only NAND gates. Such a gate is said to be *primitive* or *functionally complete*.

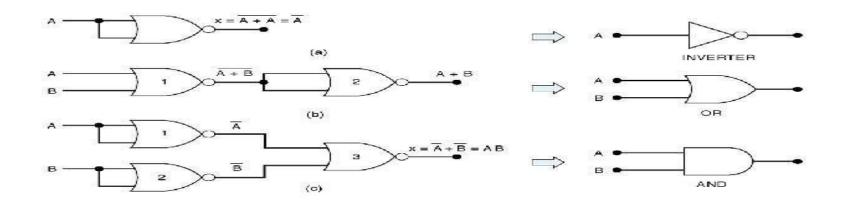

### **NAND Gates into Other Gates**

(what are these circuits?)

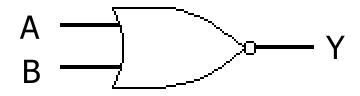

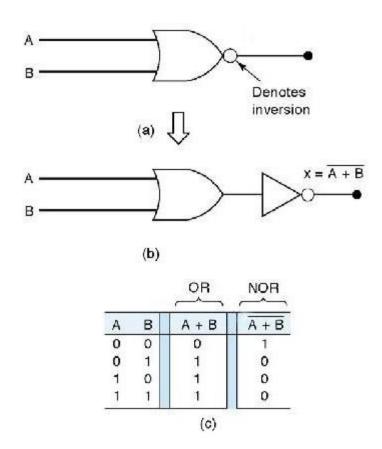

#### **The NOR Gate**

- ° This is a NOR gate. It is a combination of an OR gate followed by an inverter. It's truth table shows this...

- NOR gates also have several interesting properties...

- NOR(a,a)=(a+a)'=a'=NOT(a)

- NOR'(a,b)=(a+b)'' = a+b = OR(a,b)

- NOR(a',b')=(a'+b')'=ab=AND(a,b)

| Α | В | Υ |

|---|---|---|

| 0 | 0 | 1 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 0 |

#### **Functionally Complete Gates**

- Just like the NAND gate, the NOR gate is functionally complete...any logic function can be implemented using just NOR gates.

- Both NAND and NOR gates are very valuable as any design can be realized using either one.

- ° It is easier to build an IC chip using all NAND or NOR gates than to combine AND,OR, and NOT gates.

- NAND/NOR gates are typically faster at switching and cheaper to produce.

#### **NOR Gates into Other Gates**

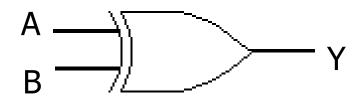

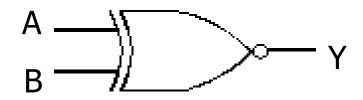

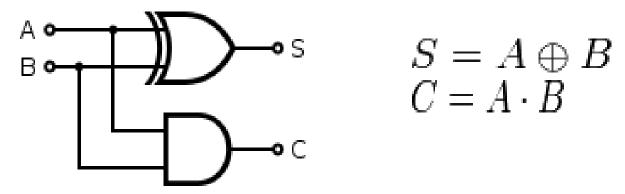

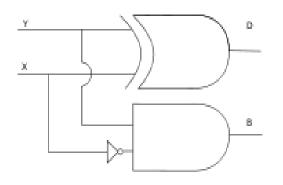

#### The XOR Gate (Exclusive-OR)

- ° This is a XOR gate.

- XOR gates assert their output

when exactly one of the inputs

is asserted, hence the name.

- ° The switching algebra symbol for this operation is  $\oplus$ , i.e.  $1 \oplus 1 = 0$  and  $1 \oplus 0 = 1$ .

| Α | В | Υ |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

#### **The XNOR Gate**

- ° This is a XNOR gate.

- This functions as an exclusive-NOR gate, or simply the complement of the XOR gate.

- The switching algebra symbol for this operation is ⊙, i.e.

1 ⊙ 1 = 1 and 1 ⊙ 0 = 0.

| Α | В | Υ |

|---|---|---|

| 0 | 0 | 1 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 1 |

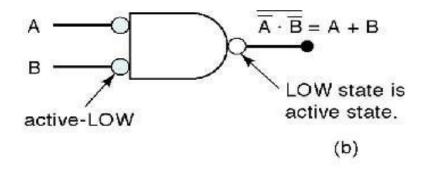

## **NOR Gate Equivalence**

° NOR Symbol, Equivalent Circuit, Truth Table

### **DeMorgan's Theorem**

° A key theorem in simplifying Boolean algebra expression is DeMorgan's Theorem. It states:

$$(a + b)' = a'b'$$

$(ab)' = a' + b'$

° Complement the expression

$$a(b + z(x + a'))$$

and simplify.

$$(a(b+z(x+a')))' = a' + (b + z(x + a'))'$$

$$= a' + b'(z(x + a'))'$$

$$= a' + b'(z' + (x + a')')$$

$$= a' + b'(z' + x'a'')$$

$$= a' + b'(z' + x'a)$$

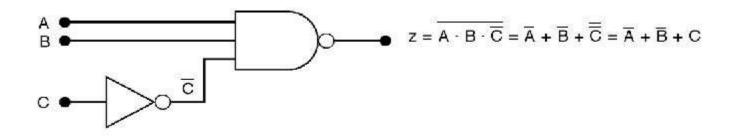

### **Example**

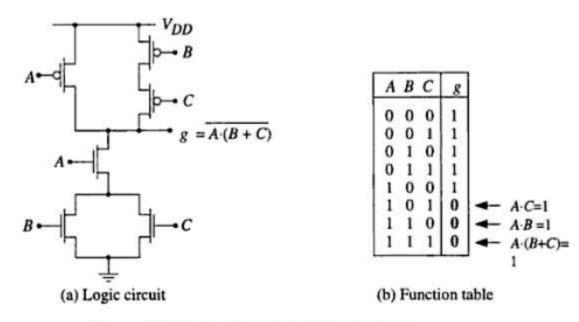

° Determine the output expression for the below circuit and simplify it using DeMorgan's Theorem

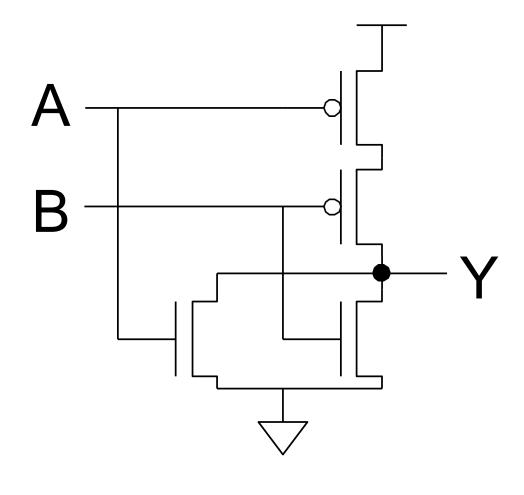

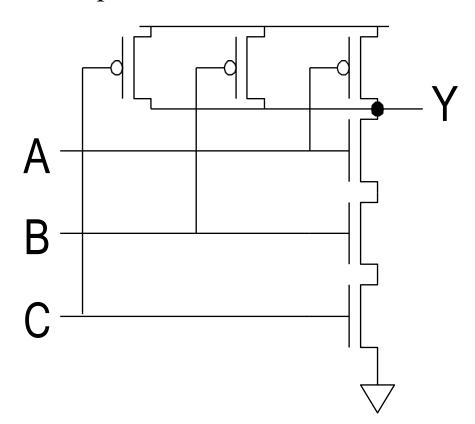

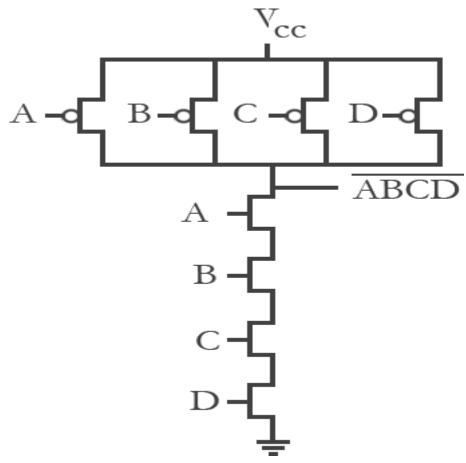

### **Universality of NAND and NOR gates**

#### Universality of NOR gate

Equivalent representations of the AND, OR, and NOT gates

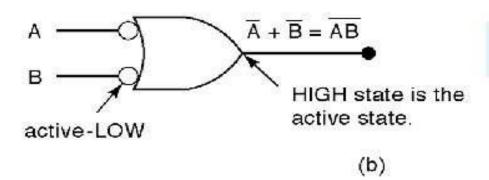

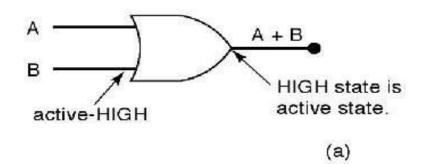

#### <u>Interpretation of the two NAND gate symbols</u>

Output goes LOW only when all inputs are HIGH.

(a)

Output is HIGH when any input is LOW.

#### Interpretation of the two OR gate symbols

Output goes HIGH when any input is HIGH.

Output goes LOW only when all inputs are LOW.

#### **Summary**

- Basic logic functions can be made from NAND, and NOR functions

- ° The behavior of digital circuits can be represented with waveforms, truth tables, or symbols

- ° Primitive gates can be combined to form larger circuits

- Boolean algebra defines how binary variables with NAND, NOR can be combined

- DeMorgan's rules are important.

- Allow conversion to NAND/NOR representations

# More Boolean Algebra

#### **Overview**

- ° Expressing Boolean functions

- ° Relationships between algebraic equations, symbols, and truth tables

- ° Simplification of Boolean expressions

- ° Minterms and Maxterms

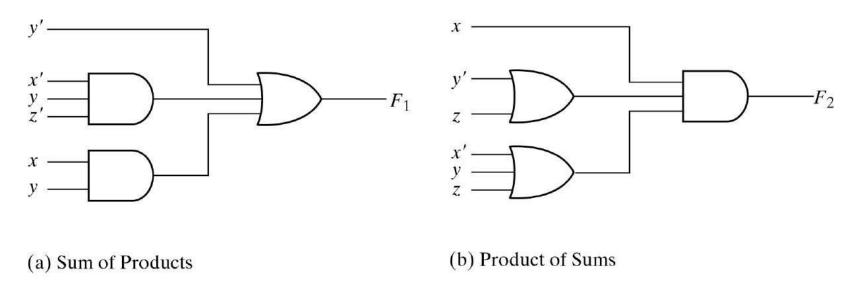

- ° AND-OR representations

- Product of sums

- Sum of products

#### **Boolean Functions**

- Boolean algebra deals with binary variables and logic operations.

- ° Function results in binary 0 or 1

| У | Z                          | F                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|---|----------------------------|-----------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0 | 0                          | 0                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 0 | 1                          | 0                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 1 | 0                          | 0                                             | ×                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 1 | 1                          | 0                                             | y                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 0 | 0                          | 1                                             | $z \longrightarrow y+z'$ $F = x(y+z')$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 0 | 1                          | 0                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 1 | 0                          | 1                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 1 | 1                          | 1                                             | F = x(y+z')                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|   | 0<br>0<br>1<br>1<br>0<br>0 | 0 0<br>0 1<br>1 0<br>1 1<br>0 0<br>0 1<br>1 0 | 0       0         0       1         1       0         1       1         0       0         1       0         0       0         1       0         1       0         1       0         1       0         1       0         1       0         1       0         1       0         1       0         1       0         1       0         1       0         1       0         1       0         1       0         1       0         1       0         1       0         1       0         1       0         1       0         1       0         1       0         1       0         1       0         1       0         1       0         1       0         1       0         1       0         1       0         1 |

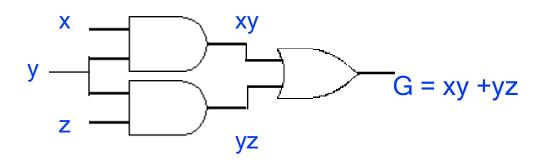

#### **Boolean Functions**

- Boolean algebra deals with binary variables and logic operations.

- ° Function results in binary 0 or 1

| X | У | Z | хy | yz | G |

|---|---|---|----|----|---|

| 0 | 0 | 0 | 0  | 0  | 0 |

| 0 | 0 | 1 | 0  | 0  | 0 |

| 0 | 1 | 0 | 0  | 0  | 0 |

| 0 | 1 | 1 | 0  | 1  | 1 |

| 1 | 0 | 0 | 0  | 0  | 0 |

| 1 | 0 | 1 | 0  | 0  | 0 |

| 1 | 1 | 0 | 1  | 0  | 1 |

| 1 | 1 | 1 | 1  | 1  | 1 |

We will learn how to transition between equation, symbols, and truth table.

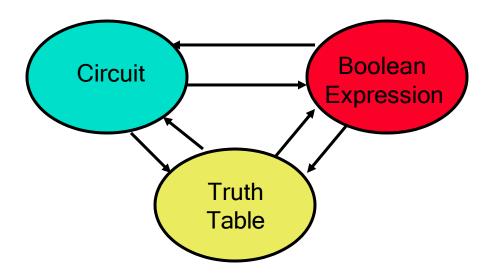

#### **Representation Conversion**

- ° Need to transition between boolean expression, truth table, and circuit (symbols).

- ° Converting between truth table and expression is easy.

- ° Converting between expression and circuit is easy.

- More difficult to convert to truth table.

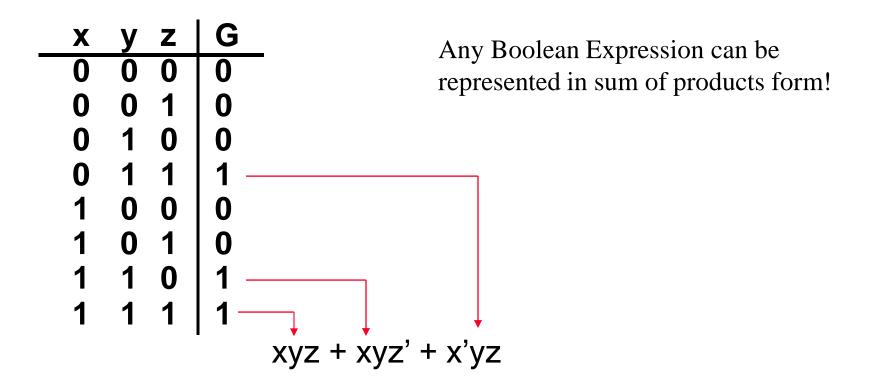

### **Truth Table to Expression**

- ° Converting a truth table to an expression

- Each row with output of 1 becomes a product term

- Sum product terms together.

#### **Equivalent Representations of Circuits**

- ° All three formats are equivalent

- Number of 1's in truth table output column equals AND terms for Sum-of-Products (SOP)

| X | У | Z | G |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 0 |

| 0 | 1 | 0 | 0 |

| 0 | 1 | 1 | 1 |

| 1 | 0 | 0 | 0 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 1 |

| 1 | 1 | 1 | 1 |

|   |   |   |   |

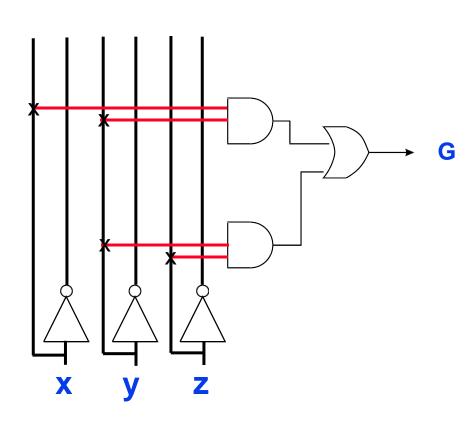

$$G = xyz + xyz' + x'yz$$

#### **Reducing Boolean Expressions**

- ° Is this the smallest possible implementation of this expression? No! G = xyz + xyz' + x'yz

- Use Boolean Algebra rules to reduce complexity while preserving functionality.

- ° Step 1: Use Theorum 1 (a + a = a)

- So xyz + xyz' + x'yz = xyz + xyz + xyz' + x'yz

- ° Step 2: Use distributive rule a(b + c) = ab + ac

- So xyz + xyz + xyz' + x'yz = xy(z + z') + yz(x + x')

- $^{\circ}$  Step 3: Use Postulate 3 (a + a' = 1)

- So xy(z + z') + yz(x + x') = xy.1 + yz.1

- $^{\circ}$  Step 4: Use Postulate 2 (a . 1 = a)

- So xy.1 + yz.1 = xy + yz = xyz + xyz' + x'yz

#### **Reduced Hardware Implementation**

- ° Reduced equation requires less hardware!

- ° Same function implemented!

| X | У | Z | G |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 0 |

| 0 | 1 | 0 | 0 |

| 0 | 1 | 1 | 1 |

| 1 | 0 | 0 | 0 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 1 |

| 1 | 1 | 1 | 1 |

$$G = xyz + xyz' + x'yz = xy + yz$$

#### **Minterms and Maxterms**

For example.

- Each variable in a Boolean expression is a literal

- Boolean variables can appear in normal (x) or complement form (x')

- Each AND combination of terms is a minterm

- ° Each OR combination of terms is a maxterm

|             |             |             | terms                    |                |             | F           |             | xample:<br>terms           |       |

|-------------|-------------|-------------|--------------------------|----------------|-------------|-------------|-------------|----------------------------|-------|

| x<br>0<br>0 | y<br>0<br>0 | z<br>0<br>1 | Minte<br>x'y'z'<br>x'y'z | $m_0$          | x<br>0<br>0 | y<br>0<br>0 | z<br>0<br>1 | Maxterr<br>x+y+z<br>x+y+z' | $M_0$ |

| 1           | 0           | 0           | xy'z'                    | m <sub>4</sub> | 1           | 0           | 0           | x'+y+z                     | $M_4$ |

| 1           | 1           | 1           | xyz                      | m <sub>7</sub> | <br>1       | 1           | 1           | x'+y'+z'                   | $M_7$ |

### **Representing Functions with Minterms**

- Minterm number same as row position in truth table (starting from top from 0)

- Shorthand way to represent functions

| X | y | Z | G |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|---|---|---|---|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0 | 0 | 0 | 0 | G = xyz + xyz' + x'yz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|   |   | 1 |   | \(\frac{1}{2} \cdot \frac{1}{2} \cdot \frac{1}{2 |

| 0 | 1 | 0 | 0 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 0 | 1 | 1 | 1 | $C = m_{-} + m_{-} = \Sigma/2 + 6 = 7$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 1 | 0 | 0 | 0 | G = $m_7$ + $m_6$ + $m_3$ = $\Sigma(3, 6, 7)$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 1 | 0 | 1 | 0 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 1 | 1 | 0 | 1 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|   |   | 1 |   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

#### **Complementing Functions**

- Minterm number same as row position in truth table (starting from top from 0)

- Shorthand way to represent functions

| X | y | Z | G | G' |                                       |

|---|---|---|---|----|---------------------------------------|

| 0 | 0 | 0 | 0 | 1  | G = xyz + xyz' + x'yz                 |

| 0 | 0 | 1 | 0 | 1  | G Ay                                  |

| 0 | 1 | 0 | 0 | 1  |                                       |

| 0 | 1 | 1 | 1 | 0  | G' = (xyz + xyz' + x'yz)' =           |

| 1 | 0 | 0 | 0 | 1  |                                       |

| 1 | 0 | 1 | 0 | 1  |                                       |

| 1 | 1 | 0 | 1 | 0  | Can we find a simpler representation? |

| 1 | 1 | 1 | 1 | 0  |                                       |

# **Complementing Functions**

- Step 1: assign temporary names

- b + c -> z

- (a + z)' = G'

- Step 2: Use DeMorgans' Law

- $(a + z)' = a' \cdot z'$

- ° Step 3: Resubstitute (b+c) for z

- a'.z' = a'.(b + c)'

- ° Step 4: Use DeMorgans' Law

- a'. (b + c)' = a'. (b'. c')

- Step 5: Associative rule

- a'. (b'. c') = a'. b'. c'

$$G = a + b + c$$

$G' = (a + b + c)'$

$$G = a + b + c$$

$G' = a' \cdot b' \cdot c' = a'b'c'$

### **Complementation Example**

- $^{\circ}$  Find complement of F = x'z + yz

- F' = (x'z + yz)'

- ° DeMorgan's

- F' = (x'z)'(yz)'

- ° DeMorgan's

- F' = (x''+z')(y'+z')

- ° Reduction -> eliminate double negation on x

•

$$F' = (x+z')(y'+z')$$

This format is called product of sums

#### **Conversion Between Canonical Forms**

- Easy to convert between minterm and maxterm representations

- ° For maxterm representation, select rows with 0's

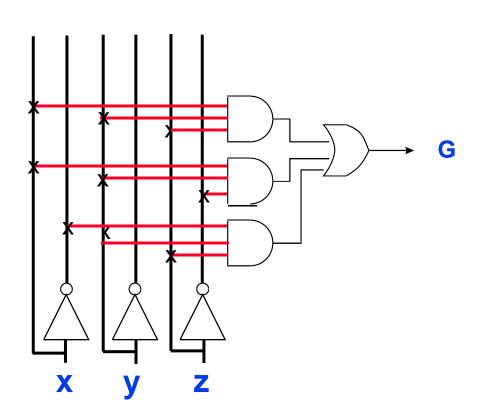

# Representation of Circuits

- ° All logic expressions can be represented in 2-level format

- ° Circuits can be reduced to minimal 2-level representation

- ° Sum of products representation most common in industry.

Fig. 2-3 Two-level implementation

# **Summary**

- ° Truth table, circuit, and boolean expression formats are equivalent

- ° Easy to translate truth table to SOP and POS representation

- ° Boolean algebra rules can be used to reduce circuit size while maintaining function

- ° All logic functions can be made from AND, OR, and NOT

- ° Easiest way to understand: Solve examples!

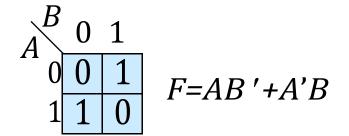

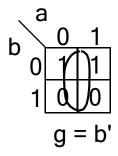

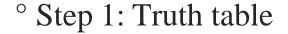

# **Minimization with Karnaugh Maps**

# <u>Overview</u>

- ° K-maps: an alternate approach to representing Boolean functions

- ° K-map representation can be used to minimize Boolean functions

- ° Easy conversion from truth table to K-map to minimized SOP representation.

- ° Simple rules (steps) used to perform minimization

- ° Leads to minimized SOP representation.

- Much faster and more more efficient than previous minimization techniques with Boolean algebra.

# Karnaugh maps

- Alternate way of representing Boolean function

- All rows of truth table represented with a square

- Each square represents a minterm

- Easy to convert between truth table, K-map, and SOP

- Unoptimized form: number of 1's in K-map equals number of minterms (products) in SOP

- Optimized form: reduced number of minterms

$$\begin{array}{c|cccc}

& y & \hline

& y & \hline

& 0 & \hline

& 1 & \\

& 0 & x'y' & x'y \\

& x & 1 & xy' & xy

\end{array}$$

$$F = \Sigma(m_0, m_1) = x'y + x'y'$$

| × <sup>y</sup> | 0 | 1 |

|----------------|---|---|

| 0              | 1 | 1 |

| 1              | 0 | 0 |

| X | У | F |

|---|---|---|

| 0 | 0 | 1 |

| 0 | 1 | 1 |

| 1 | 0 | 0 |

| 1 | 1 | 0 |

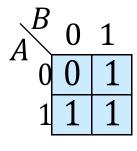

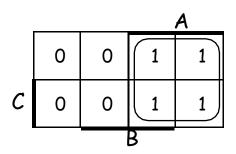

### **Karnaugh Maps**

- ° A Karnaugh map is a graphical tool for assisting in the general simplification procedure.

- ° Two variable maps.

$$F=AB+A'B+AB'$$

° Three variable maps.

$$F=AB'C'+AB'C+ABC+ABC'+A'B'C+A'BC'$$

### Rules for K-Maps

- We can reduce functions by circling 1's in the K-map

- Each circle represents minterm reduction

- Following circling, we can deduce minimized and-or form.

#### Rules to consider

ÊEvery cell containing a 1 must be included at least once.

ËThe largest possible "power of 2 rectangle" must be enclosed.

The 1's must be enclosed in the smallest possible number of rectangles.

Example

# Karnaugh Maps

- ° A Karnaugh map is a graphical tool for assisting in the general simplification procedure.

- ° Two variable maps.

$$A = \begin{bmatrix} B & 0 & 1 \\ 0 & 0 & 1 \end{bmatrix}$$

$F = AB + A'B + AB'$   $1 = A + B$

° Three variable maps.

$$F=AB'C'+AB'C+ABC+ABC'+A'B'C+A'BC'$$

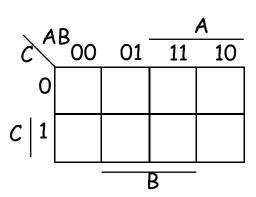

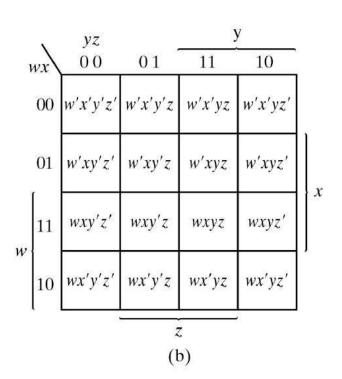

### Karnaugh maps

#### ° Numbering scheme based on Gray-code

- e.g., 00, 01, 11, 10

- Only a single bit changes in code for adjacent map cells

- This is necessary to observe the variable transitions

$$G(A,B,C) = A$$

$$\begin{array}{c|ccccc}

& A \\

\hline

1 & 0 & 0 & 1 \\

\hline

C & 0 & 0 & 1 & 1 \\

\hline

B & & & & \\

\end{array}$$

$$F(A,B,C) = \sum m(0,4,5,7) = AC + B'C'$$

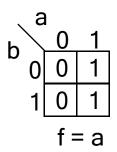

### More Karnaugh Map Examples

#### ° Examples

|   | ( al | b  |     |     |    |

|---|------|----|-----|-----|----|

| С |      | 00 | 01  | 11  | 10 |

|   | 0    | 0  | 0   | 1   | 1  |

|   | 1    | 0  | 0   | 1   | 1  |

|   | •    |    | f = | : a |    |

- 1. Circle the largest groups possible.

- 2. Group dimensions must be a power of 2.

- 3. Remember what circling means!

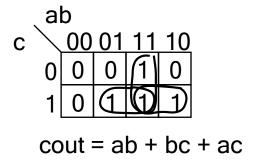

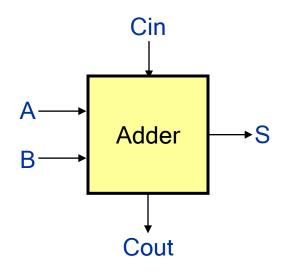

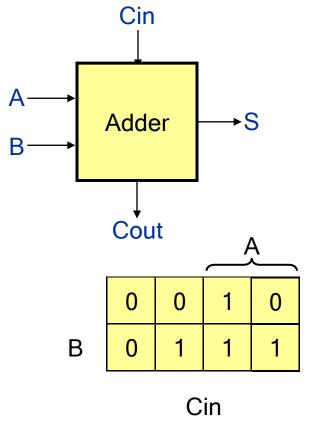

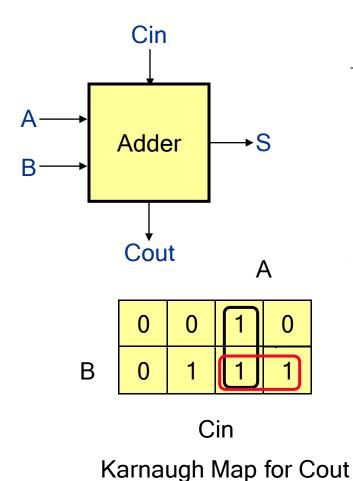

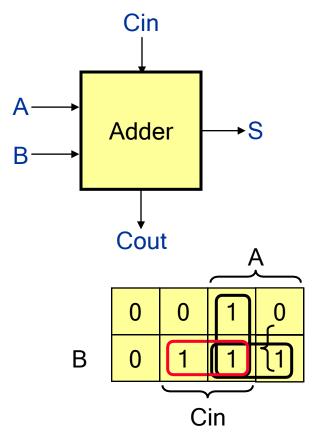

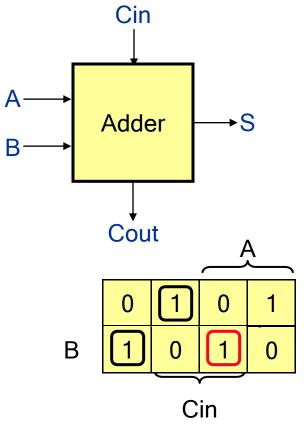

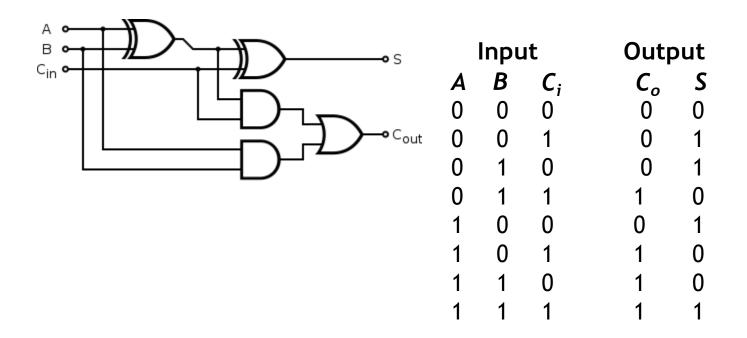

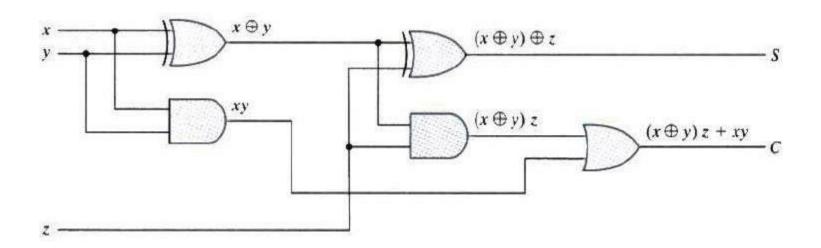

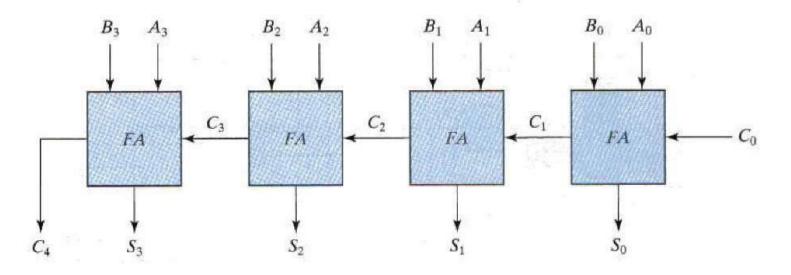

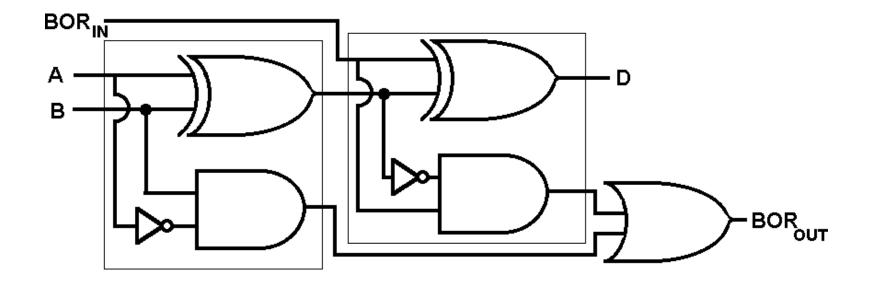

| A | В | Cin | S | Cout |

|---|---|-----|---|------|

| 0 | 0 | 0   | 0 | 0    |

| 0 | 0 | 1   | 1 | 0    |

| 0 | 1 | 0   | 1 | 0    |

| 0 | 1 | 1   | 0 | 1    |

| 1 | 0 | 0   | 1 | 0    |

| 1 | 0 | 1   | 0 | 1    |

| 1 | 1 | 0   | 0 | 1    |

| 1 | 1 | 1   | 1 | 1    |

How to use a Karnaugh Map instead of the Algebraic simplification?

$$S = A'B'Cin + A'BCin' + A'BCin + ABCin$$

$$= (A' + A)BCin + (B' + B)ACin + (Cin' + Cin)AB$$

$$= 1 \cdot BCin + 1 \cdot ACin + 1 \cdot AB$$

$$=$$

BCin + ACin + AB

| A | В | Cin | S | Cout |          |

|---|---|-----|---|------|----------|

| 0 | 0 | 0   | 0 | 0    | <b>←</b> |

| 0 | 0 | 1   | 1 | 0    | <b>←</b> |

| 0 | 1 | 0   | 1 | 0    | <b>←</b> |

| 0 | 1 | 1   | 0 | 1    | <b>←</b> |

| 1 | 0 | 0   | 1 | 0    | <b>←</b> |

| 1 | 0 | 1   | 0 | 1    | <b>←</b> |

| 1 | 1 | 0   | 0 | 1    | <b>←</b> |

| 1 | 1 | 1   | 1 | 1    | <b>←</b> |

Now we have to cover all the 1s in the Karnaugh Map using the largest rectangles and as few rectangles as we can.

| A | В | Cin | S | Cout |

|---|---|-----|---|------|

| 0 | 0 | 0   | 0 | 0    |

| 0 | 0 | 1   | 1 | 0    |

| 0 | 1 | 0   | 1 | 0    |

| 0 | 1 | 1   | 0 | _4_  |

| 1 | 0 | 0   | 1 | 0    |

| 1 | 0 | 1   | 0 | 1    |

| 1 | 1 | 0   | 0 | 1    |

| 1 | 1 | 1   | 1 | 1    |

Now we have to cover all the 1s in the Karnaugh Map using the largest rectangles and as few rectangles as we can.

Cout = ACin

Karnaugh Map for Cout

| A | В | Cin | S | Cout |

|---|---|-----|---|------|

| 0 | 0 | 0   | 0 | 0    |

| 0 | 0 | 1   | 1 | 0    |

| 0 | 1 | 0   | 1 | 0    |

| 0 | 1 | 1   | 0 | _1_  |

| 1 | 0 | 0   | 1 | 0    |

| 1 | 0 | 1   | 0 | 1    |

| 1 | 1 | 0   | 0 | 1    |

| 1 | 1 | 1   | 1 | 1    |

Now we have to cover all the 1s in the Karnaugh Map using the largest rectangles and as few rectangles as we can.

$$Cout = Acin + AB$$

| A | В | Cin | S | Cout |

|---|---|-----|---|------|

| 0 | 0 | 0   | 0 | 0    |

| 0 | 0 | 1   | 1 | 0    |

| 0 | 1 | 0   | 1 | 0    |

| 0 | 1 | 1   | 0 | 1    |

| 1 | 0 | 0   | 1 | 0    |

| 1 | 0 | 1   | 0 | 1    |

| 1 | 1 | 0   | 0 | 1    |

| 1 | 1 | 1   | 1 | 1    |

Now we have to cover all the 1s in the Karnaugh Map using the largest rectangles and as few rectangles as we can.

$$Cout = ACin + AB + BCin$$

| A | В | Cin | S | Cout |

|---|---|-----|---|------|

| 0 | 0 | 0   | 0 | 0    |

| 0 | 0 | 1   | 1 | 0    |

| 0 | 1 | 0   | 1 | 0    |

| 0 | 1 | 1   | 0 | 1    |

| 1 | 0 | 0   | 1 | 0    |

| 1 | 0 | 1   | 0 | 1    |

| 1 | 1 | 0   | 0 | 1    |

| 1 | 1 | 1   | 1 | 1    |

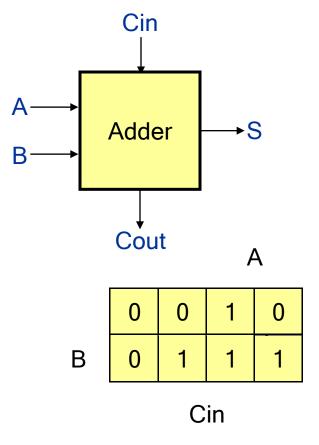

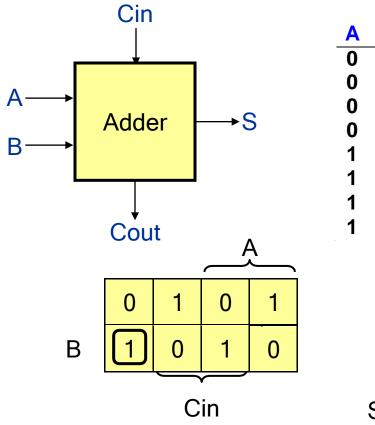

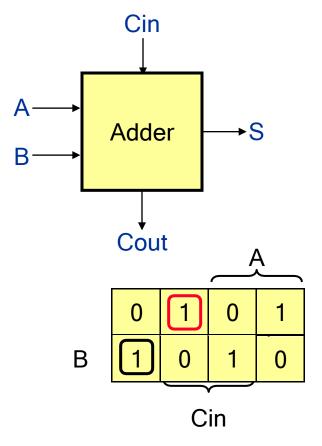

S = A'BCin'

Karnaugh Map for S

| A | В | Cin | S | Cout |

|---|---|-----|---|------|

| 0 | 0 | 0   | 0 | 0    |

| 0 | 0 | 1   | 1 | 0    |

| 0 | 1 | 0   | 1 | 0    |

| 0 | 1 | 1   | 0 | 1    |

| 1 | 0 | 0   | 1 | 0    |

| 1 | 0 | 1   | 0 | 1    |

| 1 | 1 | 0   | 0 | 1    |

| 1 | 1 | 1   | 1 | 1    |

S = A'BCin' + A'B'Cin

Karnaugh Map for S

| A | В | Cin | S | Cout |

|---|---|-----|---|------|

| 0 | 0 | 0   | 0 | 0    |

| 0 | 0 | 1   | 1 | 0    |

| 0 | 1 | 0   | 1 | 0    |

| 0 | 1 | 1   | 0 | 1    |

| 1 | 0 | 0   | 1 | 0    |

| 1 | 0 | 1   | 0 | 1    |

| 1 | 1 | 0   | 0 | 1    |

| 1 | 1 | 1   | 1 | 1    |

Karnaugh Map for S

S = A'BCin' + A'B'Cin + ABCin

Can you draw the circuit diagrams?

| A | В | Cin | S | Cout |

|---|---|-----|---|------|

| 0 | 0 | 0   | 0 | 0    |

| 0 | 0 | 1   | 1 | 0    |

| 0 | 1 | 0   | 1 | 0    |

| 0 | 1 | 1   | 0 | 1    |

| 1 | 0 | 0   | 1 | 0    |

| 1 | 0 | 1   | 0 | 1    |

| 1 | 1 | 0   | 0 | 1    |

| 1 | 1 | 1   | 1 | 1    |

Karnaugh Map for S

S = A'BCin' + A'B'Cin + ABCin + AB'Cin'

No Possible Reduction!

# <u>Summary</u>

- Karnaugh map allows us to represent functions with new notation

- ° Representation allows for logic reduction.

- Implement same function with less logic

- Each square represents one minterm

- Each circle leads to one product term

- Not all functions can be reduced

- ° Each circle represents an application of:

- Distributive rule -- x(y + z) = xy + xz

- Complement rule -x + x' = 1

# More Karnaugh Maps and Don't Cares

# **Overview**

- ° Karnaugh maps with four inputs

- Same basic rules as three input K-maps

- ° Understanding prime implicants

- Related to minterms

- ° Covering all implicants

- ° Using Don't Cares to simplify functions

- Don't care outputs are undefined

- ° Summarizing Karnaugh maps

### Karnaugh Maps for Four Input Functions

- ° Represent functions of 4 inputs with 16 minterms

- ° Use same rules developed for 3-input functions

- ° Note bracketed sections shown in example.

| $m_0$    | $m_1$    | $m_3$    | $m_2$    |

|----------|----------|----------|----------|

| $m_4$    | $m_5$    | $m_7$    | $m_6$    |

| $m_{12}$ | $m_{13}$ | $m_{15}$ | $m_{14}$ |

| $m_8$    | $m_9$    | $m_{11}$ | $m_{10}$ |

Fig. 3-8 Four-variable Map

# Karnaugh map: 4-variable example

$$^{\circ}$$

F(A,B,C,D) =  $\Box$  m(0,2,3,5,6,7,8,10,11,14,15)

F=C+A'BD+B'D'

|   |   |   |   | Α |   |

|---|---|---|---|---|---|

|   | 1 | 0 | 0 | 1 |   |

|   | 0 | 1 | 0 | 0 | D |

| _ | 1 | 1 | 1 | 1 |   |

| C | 1 | 1 | 1 | 1 |   |

| • |   |   | 3 |   | , |

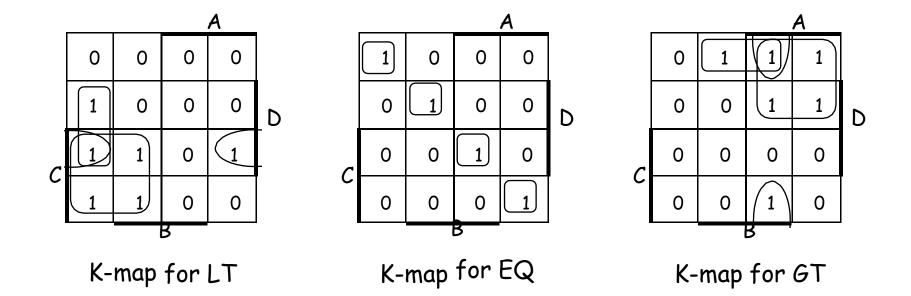

# Design examples

LT =

$$A'B'D + A'C + B'CD$$

EQ =  $A'B'C'D' + A'BC'D + ABCD + AB'CD'$

GT =  $BC'D' + AC' + ABD'$

Can you draw the truth table for these examples?

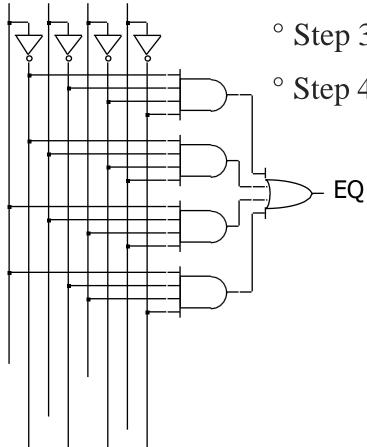

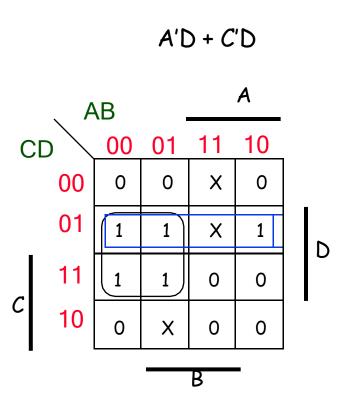

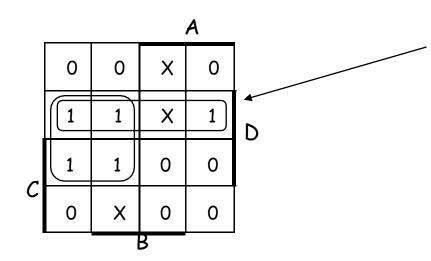

# Physical Implementation

° Step 2: K-map

° Step 3: Minimized sum-of-products

° Step 4: Physical implementation with gates

|          |   | <u> </u> |   |   |   |  |

|----------|---|----------|---|---|---|--|

|          | 1 | 0        | 0 | 0 |   |  |

|          | 0 | 1        | 0 | 0 | D |  |

| <b>~</b> | 0 | 0        | 1 | 0 |   |  |

| С        | 0 | 0        | 0 | 1 |   |  |

|          |   |          | 3 |   |   |  |

K-map for EQ

# **Karnaugh Maps**

° Four variable maps.

| CD AB 00 01 11 10 00 0 0 0 1 01 1 1 0 1 11 1 1 1 | F=A'BC'+A'CD'+ABC<br>+AB'C'D'+ABC'+AB'C<br>F=BC'+CD'+ AC+ AD' |

|--------------------------------------------------|---------------------------------------------------------------|

| 10 1 0 1 1                                       |                                                               |

- ° Need to make sure all 1's are covered

- ° Try to minimize total product terms.

- ° Design could be implemented using NANDs and NORs

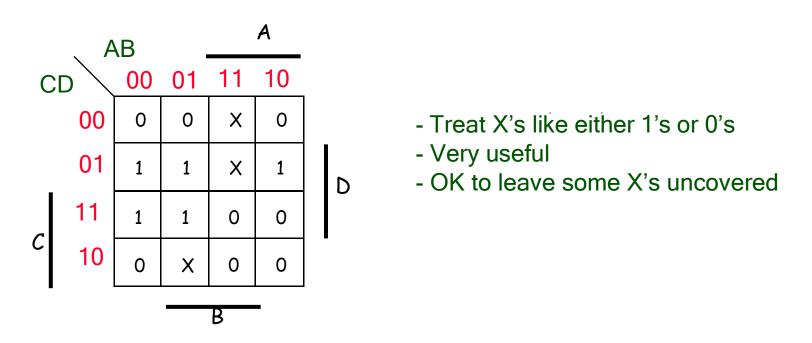

### Karnaugh maps: Don't cares

- In some cases, outputs are undefined

- ° We "don't care" if the logic produces a 0 or a 1

- This knowledge can be used to simplify functions.

### Karnaugh maps: Don't cares

- $^{\circ}$  f(A,B,C,D) = [] [] m(1,3,5,7,9) + d(6,12,13)

- without don't cares

$$-\mathbf{f} =$$

| A                                    | В | C   | D      | f                               |

|--------------------------------------|---|-----|--------|---------------------------------|

| 0                                    | 0 | 0   | 0      | 0                               |

| 0                                    | 0 | 0   | 1      | 1                               |

| 0                                    | 0 | 1   | 1<br>0 | 0                               |

| 0                                    | 0 | 1   | 1      | 1                               |

| 0                                    | 1 | 0   | 0      | 0                               |

| 0                                    | 1 | 0   | 1      | 1                               |

| 0                                    | 1 | . 1 | 0      | 0<br>1<br>0<br>1<br>0<br>1<br>X |

| 0                                    | 1 | 1   | 1      | 1                               |

| 0<br>0<br>0<br>0<br>0<br>0<br>0<br>0 | 0 | 0   | 0      | 0                               |

| 1                                    | 0 | 0   | 1      | 1                               |

| 1                                    | 0 | 1   | 0      | 0<br>1<br>0<br>0                |

| 1                                    | 0 | 1   | 1      | 0                               |

| 1                                    | 1 | 0   | 0      | X                               |

| 1                                    | 1 | 0   | 1      | X                               |

| 1                                    | 1 | 1   | 0      | 0                               |

| 1                                    | 1 | 1   | 1      | 0                               |

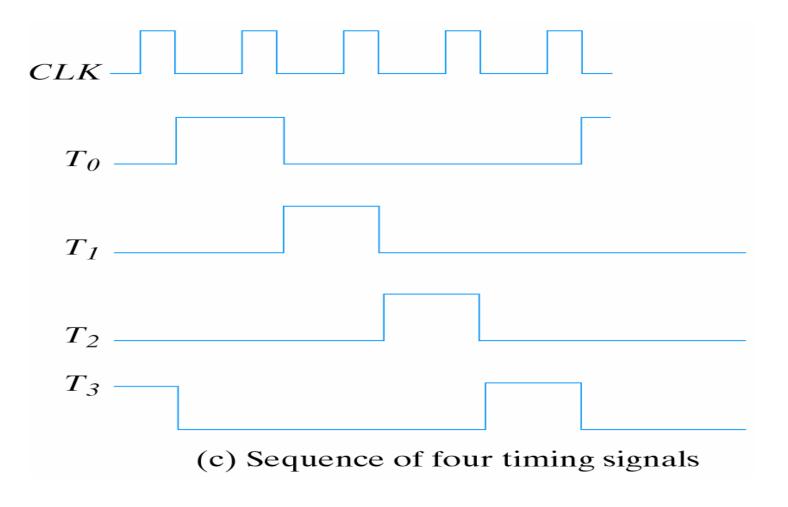

## **Don't Care Conditions**